半导体锡膏,半导体封装焊锡膏

- 半导体锡膏主要使用在封装上,鑫富锦锡膏厂家所生产的半导体封装锡膏可以使用在多种芯片IC封装上,可以达到结构与电气性能的连接,旗下众多款式锡膏产品:LED倒装固晶锡膏,mini固晶锡膏,IGBT锡膏等。

- 咨询热线:136 0301 6548

产品详情

锡膏使用在半导体中主要是封装过程中,芯片IC利用膜技术以及细微加工等技术,将芯片IC中的部件在一种框架或者基板上进行放置后固定,将各个部件进行连接导通,从内部引出需要传输信号的导电端子,并通过绝缘材料进行可塑性的罐装密封,使之构成一个具有某些功能的整体结构,这是传统意义上的封装。现在的科技技术,半导体封装是一种工程,将需要封装的器件与基板进行稳固连接,通过装配工艺形成一个完整的系统或电子产品,并能够从结构以及电性能上确保整个系统稳定工作的综合性工程。这两者形成了一种现代的广义上的半导体封装概念。

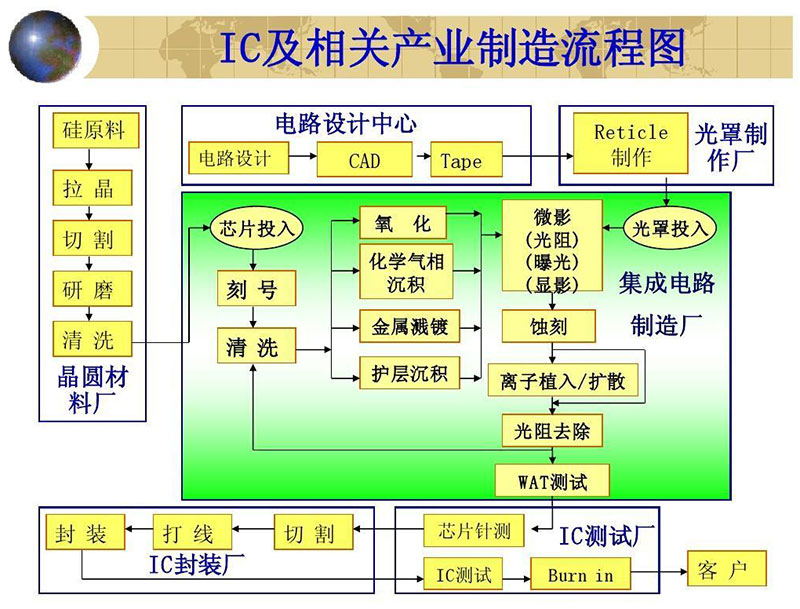

一、半导体锡膏封装芯片IC工艺流程图

二、半导体焊锡膏封装的作用

1、半导体芯片焊接领域使用的锡膏都是造价昂贵的焊料,半导体生产车间内部生产条件有严格的控制,要求车间内恒定的温湿度,严格的空气净化度控制,以及严格的防静电保护,晶片只有在这种几乎严苛的环境下生产才能够提高封装芯片的良率,因为我们所处的自然环境达不到芯片内部生产要求的严苛标准,所以芯片生产好后,需要进行封装,将已经成型的微型电路板封闭,保护内部的电路不受外部环境的影响;

2、半导体封装的另一个作用是对芯片进行支撑固定,将芯片内部的电子电路封闭后,形成一个对内部结构支撑的壳体,支撑内部线路与电子元器件,避免使用过程中震动、弯折等造成内部结构的破坏;

3、形成通路,通过引出芯片内部的引线做成IC引脚,将外部配合电路与芯片内部进行电气与结构性能的连接,形成通路,引出外部的IC引脚可以和外部电路进行电气性能上的连接,一般使用金线进行连接,载片台用于承载芯片,环氧树脂粘合剂用于将芯片粘贴在载片台上,引脚用于支撑整个器件,而塑封体则起到固定及保护作用。

4、封装形成可靠性的保护,任何的半导体芯片IC封装都需要内部与外部形成一个整体,封装后可靠性是封装工艺重要的衡量标准,芯片被制作好后离开了生产厂家严苛的环境后就容易受到外力损坏,这时候半导体封装将芯片内部完全封闭,严苛的环境被保留在内部。

三、半导体封装锡膏的使用

在完结地图规划并经工艺厂家流片后,能够选用两种办法对芯片进行功能、功能测验:一种办法是直接键合到PCB(印制电路板)上,另一种办法是经过封装厂家进行封装后,再焊接至体系中。而封装办法又可分为软封装与硬封装,软封装首要依据运用要求直接制作成模块,而硬封装则是封装成独立的芯片。

封装的办法有多种,如双列直捅封装(DIP),四方扁平封装(QEP),小外型封装(SOP),塑料引线芯片载体(PLCC)等,而封装的资料也有多种,如塑料封装、陶瓷封装等,依据不同的需求能够挑选所需的任一种封装办法,下面介绍5类常用的封装办法。

1.DIP(双列直插式封装)

DIP (Dual In-line Package),即双列直插办法封装。绝大多数中小规划集成电路(IC)均选用这种封装办法,其引脚数一般个超越100个。选用DIP封装的CPU芯片有两排引脚,需求刺进到具有DIP结构的芯片插座上,当然,也能够直接插在有相同焊孔数和几何摆放的电路板上进行焊接。DIP封装具有以下特色:

①合适在PCB上穿孔焊接,操作便利。

②芯片面积与封装面积之间的比值较大,故体积也较大。

Intel系列CPU中8088就选用这种封装办法,缓存( Cache)和前期的内存芯片也是这种封装办法。

2.QFP(四方扁平封装)

QFP (Plastic Quad Flat Package)封装的芯片引脚之间间隔很小,引脚很细,一般大规划或超大型集成电路都选用这种封装办法,其引脚数—般在100个以上。用这种办法封装的芯片有必要选用SMD (外表装置设备技能)将芯片与主板焊接起米。选用SMD装置的芯片不必在主板上打孔,一般在主板外表上有规划好的相应引脚的焊点。将芯片各引脚对准相应的焊点,即可完成与主板的焊接,用这种办法焊上去的芯片,如果不必专用工具是很难拆开下来的。QFP封装具有以下特色:

①适用于SMD外表装置技能在PCB电路板上装置布线。

②合适高频运用。

③操作便利,可靠性高。

④芯片面积与封装面积之间的比值较小。

Intel系列CPU中80286、80386和某些486土板中的芯片选用这种封装办法。

3.SOP(小外型封装)

SOP (Small Outline Package),即小外型封装。SOP封装技能由1968-1969年菲利浦公司开发成功,今后逐步派生出SOJ(J型引脚小外形封装)、TSOP(薄小外型封装)、VSOP(其小外开封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外型晶体管)、SOIC(小外型集成电路)等。SOP封装的应用规模很广,主板的频率发作器芯片就是选用SOP封装。

4.PLCC(塑料引线芯片封装)

PLCC (Plastic Leaded Chip Carrier),即塑封引线芯片封装。PLCC封装办法,外形呈正方形,四周都有引脚,外形尺寸比DIP封装小得多。PLCC封装合适用SMD外表装置技能在PCB上装置布线,具有外形尺寸小、可靠性高的长处。

5.BGA(球栅阵列封装)

BGA (Ball Grid Array Package),即球栅阵列封装。BGA封装的I/O端子以圆形或柱状焊点按阵列办法散布在封装下面,BGA技能的长处是I/O引脚数尽管添加了,但引脚间距并没有减小反而添加了,然后进步了拼装成品率;尽管它的功耗添加,但BGA能用可控塌陷芯片法焊接,然后能够改善它的电热功能;厚度和质量都较曾经的封装技能有所削减;寄生参数减小,信号传输推迟小,运用频率大人进步;组装可用共面焊接,可靠性高。

BGA与TSOP比较,具有更小的体积,更好的散热功能和电功能。BGA封装技能使每平方英寸①的存储量有了很大提高,选用BGA封装技能的内存产品在相同容量下,体积只有TSOP封装的三分之一;别的,与传统TSOP封装办法比较,BGA封装办法有愈加快速和有用的散热途径。

芯片封装后,关于芯片的引线能够简略再分为:电源线(包含参阅信号线)与地线(包含衬底衔接线)、信号输入线、信号输出线,一切这些引线及其内引线都会产牛寄生效应,而这些寄生效应关于电路功能的影响,特别是在高速高精度的电路,封装的寄生效应的影响愈加突出,因而在进行此类电路规划时有必要考虑封装的寄生效应的影响,在进行电路仿真时就需求包含一个合理的电路封装模型,同时在电路规划和地图规划时有必要采纳许多预防措施来减小封装寄生参数的影响。封装的寄生参数首要包含有:自感(内引线和外引线),外引线对地电容,外引线之间的互感以及外引线之间的电容等。

自感

一切引线(内引线及外引线)都存在必定的自感,其电感值的巨细首要取决于线的长度和封装类型,在现代封装工艺中其典型值约为2~20nH。因为电源线与地线是电路中的共用连线,在典型的混合信号lC中,因为连线自感所发作的噪声对电路的影响首要体现地电源线与地线上,即所谓的电源和地的电压“反射”或“噪声”。当电路中多个逻辑门在每个时钟跳变进行开关时,在与其相连的电源线与地线上会发作很大的噪声,所以在混合体系的地图规划中一般将模仿模块与数字模块的电源线与地线分开提供,即所谓的“模仿电源”和“数字电源”。

但是在地图规划中不可能绝对地把电源线分成模仿电源与数字电源,有时还需第三根电源线来避免模仿电源与数宁电源之间的彼此搅扰。而且能够使刚多个焊盘,多条内引线和多个封装引脚,以下降引线的等效电感。也能够运用一个大的片上电容来坚持电源VD与地之间的电压安稳。选用片上电容办法来解决自感的影响时,要注意片上电容的伉的挑选,应避免与封装电感发作频率为芯片作业频率的谐振(可经过规划几个电阻与该电容串联来破坏谐振);别的,在CMOS工艺中一般由MOS管构成该电容器,这要求晶体管很大,因而大大增大了芯片面积。与衬底(内连线也体现出自感。在现代的封装中,一般选用将管芯经过导电树脂直接固定在接地金属层上,并与几个接地的封装引脚相连,以充沛减小衬底的噪声,消除衬底连线的自感。输入信号有时也会遭到引线自感的影响,首要体现在对信号高频成分的衰减上,也会表现在瞬态波形中会发作严重的阻尼振荡,然后影响信号的安稳。

互感

内引线和外引线上的瓦感会把一些噪声耦合到灵敏信号中,然后对信号发作影响,关于模仿电源和模仿输入都易受数字电源的噪声或时钟线的跳变等影响,此时有必要对焊盘结构和位置进行认真的规划,以减小互感的影响。减小互感的办法首要有两种:一是使引线衔接时相互笔直;二是在灵敏信号的内引线之间刺进相对安稳的地线或电源线。当然关于多个并联线,也可规划成被地线包围,以减小互感效应,以至于忽略不计。同理,在地图规划时也可减小互感,即在布线时把两条电流方向相反的引线并排在一起,就可利用互感来减小自感。所以在规划焊盘结构时应充沛利用这个性质。

别的每个外引线对地都存在寄生电容,即所谓的自感和互感电容,这可能会约束电路的输入带宽或许添加前一级的负载。更重要的是,这一电容与内引线、外引线上的总电感将发作必定的谐振频率,这一频率能够被电路中不同的瞬态电流所鼓励。因为内引线和外引线的串联

电阻较小,因而其品质因数(Q)很大,这会引起强烈的谐振,然后显著地扩大了噪声。外引线之间的电容会导致线问的附加耦合,这也有必要包含在仿真中。

四、鑫富锦封装芯片锡膏生产厂家

鑫富锦锡膏厂家十年生产经验,一直致力于半导体、电子产品、LED等电子组装材料的研发和生产,旗下众多款式锡膏产品:LED倒装固晶锡膏,mini固晶锡膏,IGBT锡膏等,致力于生产可靠性高,良率高,质优价廉的不同电子封装材料。

管理员

该内容暂无评论